文章编号: 1674-8085(2017)01-0049-07

## VPR 的 FPGA 结构描述文件的解析研究

\*冷 明<sup>1</sup>, 孙凌宇<sup>1</sup>, 周 宇<sup>2</sup>, 朱 平<sup>1</sup>

(1.井冈山大学电子与信息工程学院,江西,吉安 343009; 2. 井冈山大学网络信息中心,江西,吉安 343009)

摘 要:作为描述 FPGA 硬件资源的结构描述文件,不仅是 VPR 布局布线工具的重要组成元素,而且是 FPGA 硬软件工程师相互沟通的桥梁。阐述了 VPR 布局布线的工作流程,对 VPR 的 FPGA 结构描述文件进行解析,以正确地表示 FPGA 芯片内部的通道、开关、逻辑资源、布线资源等结构信息。进而,以可配置逻辑块 CLB 和 Virtex-6 的 Slice 结构为例,分别给出了相应的 FPGA 结构描述文件,重点讨论了<pb\_type>逻辑单元块和<interconnect>内部连接的 XML 代码。FPGA 结构描述文件正确地被描述和解析,有助于开展 FPGA 结构在内存物理中的存储和转换等后续研究工作。

关键词: VPR; 现场可编程门阵列; 结构描述文件; 解析

中图分类号: TP391

文献标识码: A

DOI:10.3969/j.issn.1674-8085.2017.01.010

## RESEARCH ON PARSE OF FPGA ARCHITECTURE DESCRIPTION FILE OF VPR

\* LENG Ming, SUN Ling-yu, ZHOU Yu, ZHU Ping

(1. School of Electronics and Information Engineering, Jinggangshan University, Ji'an, Jiangxi 343009, China;

2. Center of network information, Jinggangshan University, Ji'an 343009, China)

**Abstract:** As the communication channel between the hardware engineer and software engineer, FPGA architecture description file is crucial component of **V**ersatile **P**lacement and **R**outing tool (VPR) which is used to describe FPGA hardware resources. We present the placement and routing process of VPR. We also parse the FPGA architecture description file of VPR to make sure that we can accurately denote channels, switches, logic resources, routing resources and others architecture information inside the FPGA chip. Furthermore, we give the corresponding the FPGA architecture description files of configurable logic block and Virtex-6 slice. We also discuss the XML codes of physical blocks and intra-block interconnects. It is important to do research on its memory storage format and conversion that we can accurately parse the FPGA architecture description file.

**Key words:** versatile placement and routing; FPGA; architecture description file; parse

### 0 引言

自 Xilinx 公司首次上市 FPGA 以来, FPGA 从

最初的 1200 个可用门电路规模,到上世纪末的几十万门电路规模,再到最新的 Virtex®-7 系列的千万门电路规模,FPGA 的集成度不断地提高。相比硬接线固定模式的专用集成电路 ASIC,使用可编程

收稿日期: 2016-08-03; 修改日期: 2016-12-13

基金项目: 国家自然科学基金项目(61363014); 江西省青年科学家培养对象计划(20153BCB23003); 江西省科技厅科技支撑项目(20132BBE50048); 江西省自然科学基金项目(20161BAB202050); 江西省教育厅科学技术研究项目(GJJ150779,GJJ16079)

作者简介: \*冷 明(1975-), 男, 教授, 博士, 主要从事 VLSI 算法分析与设计, 组合分析与优化等方面的研究(E-Mail: lengming@jgsu.edu.cn);

孙凌宇(1976-),女,教授,硕士,主要从事电子设计自动化,组合算法等方面的研究(E-Mail: lzylmsly@gmail.com);

周 字(1974-), 男,高级实验师,硕士,主要从事组合分析与优化方面的研究(E-Mail: zy@jgsu.edu.cn);

朱 平(1955-),男,教授,硕士,主要从事算法分析与设计方面的研究((E-Mail: zhuping810@163.com).

模式 FPGA 器件设计的电子产品具有响应时间快、设计成本低、研发周期短、可重复配置、稳定性强等优点,在超高速传输、数字信号处理、汽车电子、医疗和工业控制等领域均得到了广泛应用。

随着超大规模集成电路技术的发展,VLSI 的制造工艺已从深亚微米工艺时代进入纳米工艺时代,国际半导体技术蓝图报告[1]预测 2020 年 VLSI 特征尺寸将减少到 5 nm。现场可编程门阵列 FPGA 的规模急剧增加,极大地扩充了 FPGA 中逻辑功能模块的种类和数量,集成了越来越多的 IP 模块,如 FIFO/RAM/ROM 等片上存储器、PLL/DLL 锁相环、高速串行收发器、嵌入式 CPU 和 DSP 处理器等,极大地提升了 FPGA 器件应用的灵活性和硬件并行的处理性能。

VPR (Versatile Placement and Routing for FPGAs) 是由加拿大多伦多大学 Jason 和 Jonatha 教 授等开发的,集 FPGA 布局和布线为一体的开发探 索、架构参数、性能评估功能的最新 EDA 工具, 获得了 FPGA 学术界和工业界最广泛的认可,为 FPGA 架构研究提供了便利手段[2-3]。研究人员根据 FPGA 结构研究和设计的需要,通过布局布线测试 对所提出的 FPGA 结构进行验证,通过测试数据评 价该芯片结构并调整优化 FPGA 的结构参数。FPGA 结构描述文件作为 FPGA 硬件平台、FPGA 布局布 线工具、FPGA 硬件软件 IP 核、FPGA 开发板之间 相互沟通的桥梁,其应用相当广泛,例如:根据 FPGA 结构描述文件构建相应的布线资源图,用于 基于 FPGA 互连资源的布线模块; FPGA 结构描述 文件被位流文件生成模块用于生成相应的位流文 件[4]。

本文通过阐述 VPR 布局布线的工作流程,可以发现使用 FPGA 的结构描述文件正确合理地描述 FPGA 硬件资源,是 VPR 布局布线过程中重要的环节。针对 FPGA 结构研究的需要,对 VPR 的结构描述文件进行解析,从而获得 FPGA 芯片内部的通道、开关、逻辑资源、布线资源等结构信息。进而,以可配置逻辑块 CLB 和 Virtex-6 型号 Slice 结构为例,分别给出了相应的 FPGA 结构描述文件,重点

讨论了<pb\_type>逻辑单元块和<interconnect>内部连接的 XML 代码。

### 1 VPR 的 FPGA 结构描述文件的解析

#### 1.1 VPR 的工作流程

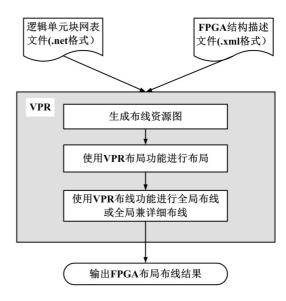

图 1 VPR 的工作流程图<sup>[2-3]</sup>

Fig.1 The workflow diagram of VPR<sup>[2-3]</sup>

VPR 的工作流程图如图 1 所示。VPR 输入 FPGA 设计的逻辑单元块网表文件和 FPGA 硬件资 源的结构描述文件。其中, FPGA 设计采用".net" 格式的逻辑单元块网表文件来表示,存储所需要布 局布线的逻辑网表; FPGA 硬件资源采用".xml" 格式的结构描述文件来表示,存储 FPGA 芯片的版 图和布线结构<sup>[2]</sup>。首先, VPR 对 FPGA 结构描述文 件进行词法语法分析和中间代码生成,解析生成相 应的布线资源图。然后, VPR 依据网表文件构造 FPGA 设计相应的逻辑网表,实现逻辑网表在物理 存储空间中的表示,进而对逻辑网表完成布局;在 完成布局后, VPR 在布线资源图上, 按照布线算法 进行全局布线或者全局兼详细布线[3]。由此可见, 正确完整地描述 FPGA 硬件资源并生成相应的 FPGA 结构描述文件,是 VPR 布局布线过程中重要 的环节。

#### 1.2 VPR 的 FPGA 结构描述文件的解析

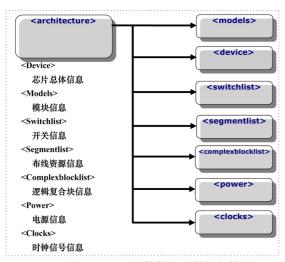

图 2 FPGA 结构描述文件的架构图

Fig.2 The architecture diagram of VPR architecture description file

VPR的FPGA结构描述文件采用XML可扩展标记语言来描述FPGA芯片内部的通道、开关、逻辑资源、布线资源等结构信息,具有易于掌握和使用、形式与内容分离、解析器开放源代码、良好的扩展性等优点<sup>[5]</sup>。XML文件以层次化嵌套的开始标签和结束标签组成,每组标签内有附加说明和可选择的属性值和内容。

FPGA 结构描述文件的架构如图 2 所示,以 <architecture>作为根标记,对应一个 FPGA 硬件设计,它包含<device>芯片总体信息、<models>模块信息、<switchlist>开关信息、<segmentlist>布线资源信息、<complexblocklist>逻辑复合块信息、<power>电源信息和<clocks>时钟信号信息<sup>[6]</sup>。

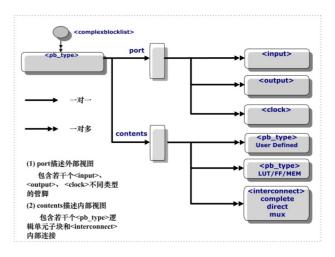

FPGA 结构描述文件的<complexblocklist>组成如图 3 所示,<complexblocklist>包含若干个<pb\_type>逻辑单元块;每个逻辑单元块<pb\_type>由 port 和 contents 两部分组成,其中 port 描述外部视图,包含若干个<input>、<output>、<clock>不同类型的管脚,且管脚可以指定 port\_class 属性为地址信号(address)、输入数据信号(data\_in)、输出数据信号(data\_out)、写使能信号(write\_en)和时钟信号(clock); contents 描述内部视图,包含若干个<pb\_type>逻辑单元子块和<interconnect>内部连接。<pb\_type>逻辑单元块可以指定 class 属性为查找表(lut)、触发器(flipflop)和存储器(memory)。<interconnect>内部连接包含<complete>全互连、<direct>直连、<mux>多路选择连接三种类型。

图 3 FPGA 结构描述文件的<complexblocklist>组成图 Fig. 3 The <complexblocklist> component diagram of VPR architecture description file

# 2 可配置逻辑块 CLB 的 FPGA 结构描述文件

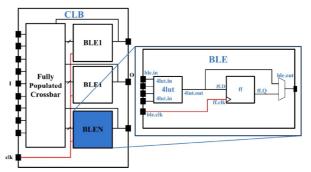

图 4 FPGA 可配置逻辑块 CLB 的模型 Fig.4 The model of FPGA configurable logic block

以图 4 描述的某 FPGA 可配置逻辑块 CLB 为例,其 FPGA 结构描述代码如表 1 所示,构成了 <pb\_type>逻辑单元块定义的嵌套。在外层的 <pb\_type>是包含 22 位输入信号 I,10 位输出信号 O,1 位时钟信号 clk 的 CLB; 内部包含了 10 个 <pb\_type name="ble"> 基 本 逻 辑 单 元 和 <interconnect>内部连接; <interconnect>包含了 1 个 32\*40 位全互连、1 个 1\*10 位全互连和 1 个 10\*10 位直连。在内层的<pb\_type name="ble">是 4 位输入信号 in,1 位输出信号 out,1 位时钟信号 clk 的 BLE; 内 部 逻 辑 单 元 子 块 包 含 了 1 个 <pb\_type name="4lut">4 位查找表、1 个<pb\_type name="ff">1 个 <pb\_type name="ff">1 个 1\*1 位触发器; <interconnect>内部连接包含了 1 个 1\*1 位直连、1 个 4\*4 位直连、1 个 2 选 1 多路选择连接和 1 个 1\*1 位直连。

### 表 1 FPGA 可配置逻辑块 CLB 的结构描述代码

Table 1 The architecture description code of FPGA configurable logic block

| 逻辑模块                                 | 逻辑模块内部特性                                                                    | 逻辑模块描述代码                                                                                                                                                                                                            |  |

|--------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLB<br>(Configurable<br>Logic Block) | CLB 的管脚特性 22 位输入 10 位输出 1 位时钟信号  CLB 的内部连接特性 32*40 位全互连 1*10 位全互连 10*10 位直连 | <pre><pb_type name="clb"></pb_type></pre>                                                                                                                                                                           |  |

| BLE<br>(Basic Logic<br>Element)      | BLE 的管脚特性<br>4 位输入<br>1 位输出<br>1 位时钟信号<br>BLE 的内部连接特性<br>1*1 位直连<br>4*4 位直连 | <pre><pb_type name="ble" num_pb="10"></pb_type></pre>                                                                                                                                                               |  |

|                                      | 2 选 1 多路选择连接<br>1*1 位直连                                                     | <direct input="ble.ble_clk" output="ff.ff_clk"></direct>                                                                                                                                                            |  |

|                                      | 4 位 LUT                                                                     | <pre><pb_type blif_model=".names" class="lut" name="4lut" num_pb="1"> <input name="4lut_in" num_pins="4" port_class="lut_in"/> <output name="4lut_out" num_pins="1" port_class="lut_out"></output> </pb_type></pre> |  |

|                                      | 1 位 Flipflop                                                                | <pre><pb_type blif_model=".latch" class="flipflop" name="ff" num_pb="1"></pb_type></pre>                                                                                                                            |  |

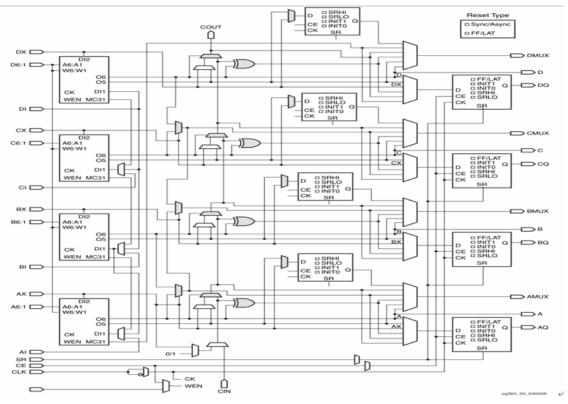

### 3 Xilinx 公司 Virtex-6 型号 Slice 的 FPGA 结构描述文件

图 5 Xilinx 公司 Virtex-6 型号 slice 的模型<sup>[7]</sup> Fig.5 The slice model of Xilinx's Virtex-6<sup>[7]</sup>

Slice 作为 Xilinx 公司 FPGA 的基本逻辑单位,其 Virtex-6 型号 Slice 的内部结构如图 5 所示。Virtex-6 型号 FPGA 的 Slice 由 4 个六输入的查找表 LUT、4 个大触发器 FF 或锁存器 LATCH、4 个小触发器 FF、多路转换器 MUX、运算进位逻辑 CARRY 构成,其中六输入查找表 LUT 或配置为 64 位 ROM,即具有 1 个六输入的 LUT;或配置为 32 位 ROM,即具有 2 个五输入的 LUT,其不同

输出使用相同的地址或逻辑输入。Slice 中的每个 LUT 对应一个触发器,或选择性地配置为锁存器, 且其他 4 个触发器保持未使用状态;或选择性地寄 存于触发器中。Slice 的算术逻辑包括一个异或门 XORG,用于实现 2bit 全加操作;还包括一个专用 与门 MULTAND,用于提高乘法器的效率。Slice 的 进位逻辑由函数复用器 MUXC 和专用进位信号组 成,用于实现快速的算术加减法操作<sup>[7]</sup>。

表 2 Xilinx 公司 Virtex-6 型号 slice 的结构描述代码

| Table 2 The architecture description code of Xilinx's Virtex-6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 逻辑模块内部特性                                                       | 逻辑模块描述代码                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SLICE 的管脚特性                                                    | <pb name="v6 lslice" type=""></pb>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 4 组数据输入信号                                                      | <input equivalent="false" name="AX" num="" pins="1"/>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1 位置位复位信号 SR                                                   | A/AI/BX/B/BI/CX/C/CI/DX/D/DI/SR/CIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 1 位使能信号 CE                                                     | <input equivalent="false" name="CE" num="" pins="1"/>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1 位进位信号 CIN                                                    | <pre><output equivalent="false" name="AMUX" num_pins="1"></output></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1 位时钟信号 CLK                                                    | A/AQ/BMUX/B/BQ/CMUX/C/CQ/DMUX/D/DQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 4 组数据输出信号                                                      | <pre><output equivalent="false" name="COUT" num="" pins="1"></output></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 1 位进位信号 COUT                                                   | <pre><clock name="CLK"></clock></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                | <pb_type blif_model=".subcktvlut" name="lut" num_pb="4"></pb_type>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                                                | <pre><pb blif="" model=".subckt carry" name="carry" num="" pb="4" type=""></pb></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                | <pre><pb blif="" model=".subcktvffs" name="ff small" num="" pb="4" type=""></pb></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                                                | <pre><pb blif="" model=".subcktvffb" name="ff big" num="" pb="4" type=""></pb></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| SLICE 内部连接特性                                                   | <interconnect></interconnect>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ①3 个 1*8 位全互连                                                  | <pre><direct input="{v6_lslice.A v6_lslice.B v6_lslice.C v6_lslice.D}" name="lutA" output="lut.A"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| ①2 个 24*24 位直连                                                 | <pre><direct input="{v6 lslice.A v6 lslice.B v6 lslice.C v6 lslice.D}" name="lutW" output="lut.W"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| ②1 个 4*4 位直连                                                   | <pre><direct input="{v6 lslice.AX v6 lslice.BX v6 lslice.CX v6 lslice.DX}" name="lutDl2" output="lut.Dl2"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| ③1 个 1*1 位直连                                                   | <pre><direct input="v6 lslice.DI" name="DutDI1" output="lut[3].DI1"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| ④4 个 1*1 位直连                                                   | <pre><direct input="lut.O6" name="carryO6" output="carry.xor"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ⑤3 个 1*1 位直连                                                   | <pre><direct input="carry[2:0].cmux out" name="carrymuxxor" output="carry[3:1].cmuxxor"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| ⑥6 个 1*1 位直连                                                   | <pre><direct input="{lut[3].06 lut[2].06 lut[1].06 lut[1].06 lut[0].06}" name="carrymmux" output="carry[2:0].mmux"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ⑦3 个 1*1 位直连                                                   | <pre><direct input="{v6 lslice.AX v6 lslice.BX v6 lslice.CX}" name="carrymmux select" output="carry[2:0].mmux select"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| ⑧1 个 1*1 位直连<br>⑨4 个 1*1 位直连                                   | <pre><direct input="carry[3].mmux out" name="cout" output="v6 Islice.COUT"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ⑩4 个 1*1 位直连                                                   | <pre><direct input="lut[3:0].06" name="ABCD" output="{v6 lslice.D v6 lslice.C v6 lslice.B v6 lslice.A}"></direct></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| ①4 个 2 选 1 多路选择                                                | <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| ②4 个 5 选 1 多路选择                                                | <pre><mux input="v6 lslice.AX lut[0].05" name="ff smallA" output="ff small[0].D"></mux></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| ③4个6选1多路选择                                                     | <mux input="v6 lslice.BX lut[1].O5" name="ff smallB" output="ff small[1].D"></mux>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ④1个3选1多路选择                                                     | <mux input="v6 lslice.CX lut[2].O5" name="ff" output="ff" small[2].d"="" smallc"=""></mux>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ⑤1个3选1多路选择                                                     | <mux input="v6 lslice.DX lut[3].O5" name="ff" output="ff" small[3].d"="" smalld"=""></mux>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| ⑤1个5选1多路选择                                                     | <pre><mux input="lut[0].O5 lut[0].O6 carry[0].cmux out carry[0].mmux out carry[0].xor out" name="ff bigA" output="ff big[0].D"></mux></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |